功率器件的散热问题看贺利氏电子从封装角度给的妙招

半导体分立器件最重要的包含二极管,三极管,晶体管和晶闸管,从功率解决能力来分有低压小功率(电压低于200V,电流小于200mA),中功率器件(电压低于200V,电流小于5A),大功率器件(电压低于500V,电流小于40A)和高压大功率器件(电压高于600V,电流大于40A)。而大功率器件成为目前最大的热门,特别是功率快恢复二极管FRD,功率MOSFET,IGBT等,从工业控制和消费类电子拓展至变频家电,新能源,智能电网,轨道交通。而这些大功率器件的封装大多以TO系列为主(如下图所示)

近年来,由于大规模使用的硅功率器件达到起使用极限,在工作频率,功率,耐热温度,能效,耐恶劣环境及小型化方面面临瓶颈,而以氮化镓和碳化硅为代表的第三代半导体在热导率,频率转换,高温工作特性等表现出优越的物理特性。但不论是硅基功率器件,还是宽带化合物半导体功率器件,在功率器件设计过程中,热设计是必不可少的。从芯片材料选择,芯片内部结构热设计,封装热设计,管壳热设计到实际应用中的热设计。在封装工序中,芯片焊接(固晶/装片/贴片)是一道最重要的工序,是将半导体芯片通过焊接层固定在框架载板上,而焊接层除了为芯片提供机械连结和电连接外,还为芯片提供良好的散热通道,对于功率器件,这是主要的散热通道,也是功率器件热设计当中考虑的关键工序。高功率器件的贴片目前主要有共晶焊(Eutecticbonding)和软焊料焊接(softsolder)。但共晶焊通常只适用于比较小的芯片(

<1mm)在芯片背面通过pvd工艺溅射(au(as)niagauge),在400多度的高温下和有银涂层的框架焊接在一起,但对于较大的芯片,背金结合不完全,温度越高,内部应力越大,很容易产生裂片,而且背面是比较厚的金,成本也很高。软焊料焊接目前还是一个主要焊接方式,而且随着功率器件的发展,电压和功率的增加,转化效率的提升,从传统的硅基器件,第二代砷化镓,磷化铟,到现在的第三代功率器件氮化镓,碳化硅等,对焊接材料也提出了更高的要求,稳定的焊接强度,高的焊接质量和良好的导电性和散热能力。贺利氏电子深耕半导体封装领域多年,不论是传统的中低端功率器件,还是现在火热的碳化硅和氮化硅等化合物半导体,因为不同导电和散热设计要求,对相应的焊接材料有不同的要求,贺利氏电子在这方面都提供有相应的材料解决方案。

软焊料(softsolder)包括含铅焊料(高温焊料)和无铅焊料(低温焊料),是利用铅锡合金或锡银铜合金等座焊料,把背面溅射金或银(TiNiAg)的芯片焊接在镀银,镀镍或裸铜框架上,能轻松实现大约50W/m.K的导热性。现在随着欧盟和一些国家对对环保提出更高的要求,含铅焊料从历史发展的角度会最终被逐渐替代,但在极短的时间内,由于含铅焊料的高温可靠性,在被彻底禁用前,短时间之内还特别难找到性价比如此高的焊料。贺利氏电子能够给大家提供很一系列的高温含铅焊料和无铅焊料,通过客户端多年的使用,拥有非常良好的工艺稳定性,润湿性,很低的空洞率(total

<3%),高散热性,导电性和可靠性。

合金体系中,不同的金属和含量对于可靠性和润湿性等起到不同的作用,铅对于高温和可靠性起着关键作用;锡是形成金属间(IMC)的重要媒介,可以和芯片的背银以及框架的镀银或镀镍表面在熔融状态形成IMC Cu3Sn/Cu6Sn5或Ni3Sn4,提高焊接强度;银能改善表面润湿,提高强度,但含量不能太高,否则会引起焊层开裂;锑能够更好的降低表面张力,提高铅锡合金的强度。在器件使用的过程中会经常的开关,产生热量,会造成热疲劳,引起失效。根据热循环模拟能得出富铅合金焊料比富锡合金焊料有更好的可靠性。从润湿性和可靠性角度,银表面>

铜表面>

镍表面。

相对于软焊料,锡膏在生产效率和成本方面的优势,贺利氏电子也开发了针对点胶和印刷设备的锡膏焊料,独特的助焊剂体系和自有焊粉的严格管控,带来优良的锡膏特性:

良好的润湿性和分散性,如图1,2所示,低残留,无助焊剂飞溅和锡膏飞溅:对于后面的键合工艺(wirebonding)减少了因飞溅带来的虚焊(weakbond),脱焊(NSOL:non-stick on lead)等键合质量上的问题;同时也改善了芯片周围区域塑封后的分层(delamination)状况,提高可靠性;

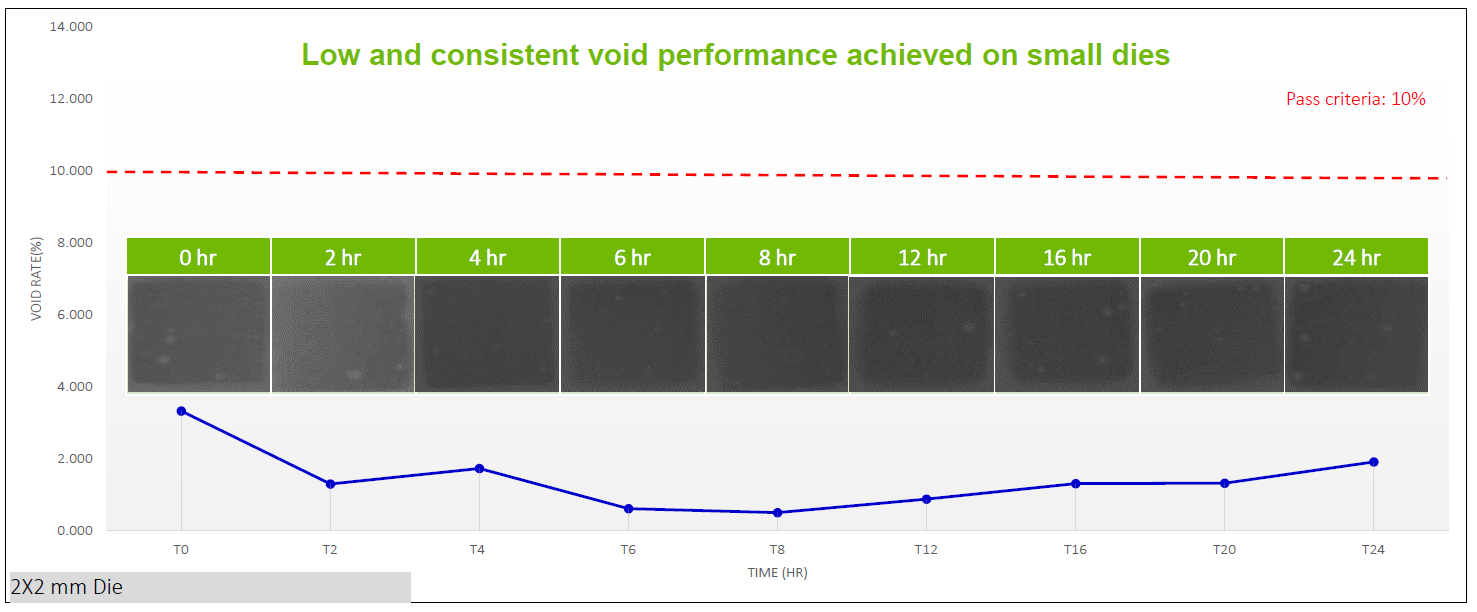

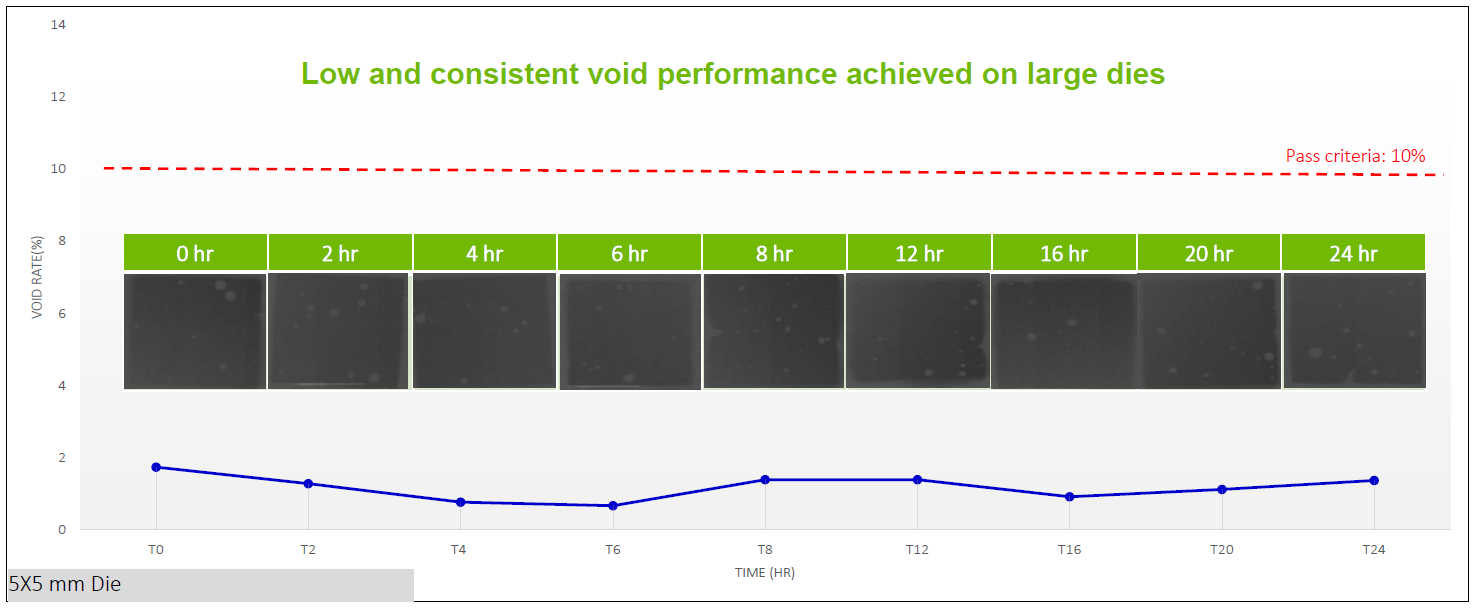

回流后极低的空洞率,如图3,4所示,这些都为功率器件良好的散热提供了保障,提高了产品的可靠性和稳定性。

锡膏由于含有助焊剂不像软焊料锡线(无助焊剂)有很好的空洞管控。而焊层空洞对功率器件热特性产生重要的影响,空洞处热导率为空气热导率5W/m.K,远低于焊料的热导率,会在此处形成“热斑”,热阻(Rth)升高。而热阻又是预测功率器件结温和可靠性的重要热参数。空洞大小,空洞的位置,再加上CTE的不匹配,在器件工作过程中产生应力,发生EOS失效(electricaloverstress)。

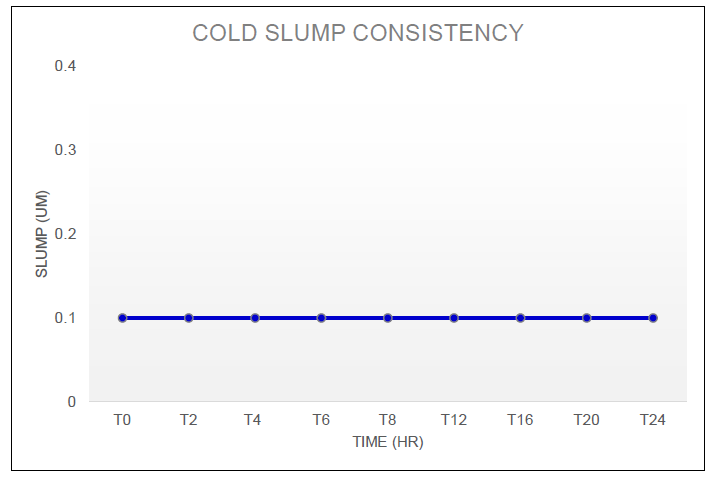

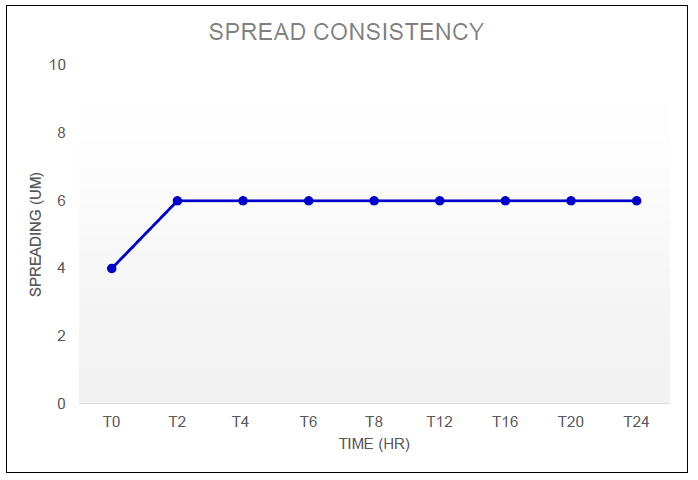

图1 和图2 表明经过24h,锡膏仍显示稳定分散性和冷坍塌,提高生产的基本工艺的可操作性;

图3 和图4显示2*2mm和5*5mm芯片经过24h空洞率处于低水平并且保持稳定。

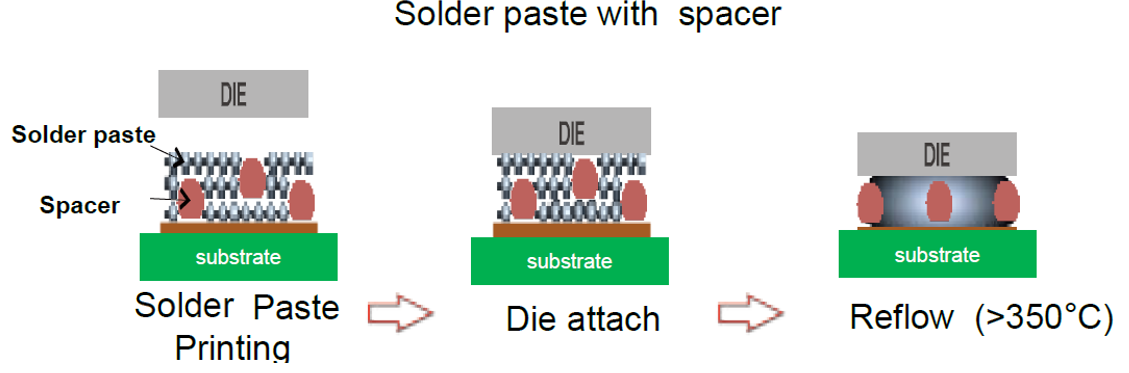

随着封装尺寸的变小,不论是从成本还时体积,对芯片的要求也是越来越薄,这样对保持BLT(bondline thickness)稳定的要求提出了新的挑战,BLT控制不好,很容易产生裂片和芯片倾斜,对后续的键合也带来影响。通过在锡膏中加入高熔点金属微球,回流后,金属球并不融化,这样在冷却后,金属球均匀分散在焊层,加入金属球一方面能够减少熔融合金和芯片的粘合力控制芯片的倾斜;另一方面能作为支撑柱,对于后面的clipbond,同样保持很好的BLT控制,维持在同一高度,如图5所示。

由于硅是间接带隙半导体,受本身半导体结构的限制,结温(junctiontemperature)最高只能到175oC,工作时候的温度限定在175oC;为了适应更高的工作时候的温度(结温)和更大的电流密度的需求,宽带隙半导体碳化硅和氮化镓满足了这一需求。相对于硅基半导体,宽带隙半导体在热导率,击穿电场,耐高温、抗辐射等方面有明显优势,如表2所示。一方面要延长硅基功率器件的使用周期,另一方面要适应碳化硅等三代半导体小型化高散热的要求,这对作为功率器件封装中关键焊接材料也提出了新的要求,一种原因是要有低的工艺温度和高的工作时候的温度,还要有很好的导电性和散热能力,传统的软焊料和锡膏就很难满足这一要求。贺利氏电子开发了烧结银焊料,锡膏中主要是金属银,银的熔点是961oC,这就保证了焊接材料可以工作在200oC以上,具有高导电性,高散热能力和热机械稳定性。从焊接工艺来说,这种烧结材料不同于锡膏,在整个焊接过程中,银始终作为固态形式存在,通过扩散将芯片背银和框架上的银(铜)连接在一起,如图6所示,烧结后具备很好的剪切强度,高的导电性和散热性,提高了功率器件的工作时候的温度和可靠性。表3给出了贺利氏电子的烧结银和其他焊料在制程控制,导电率,散热性,机械强度方面的对比,在散热方面这款无压烧结银材料具备超过100W/m.K的热导率,焊接工艺可以在通用的锡膏焊接设备实现。

作为电子组装和封装材料的顶级制造商的贺利氏电子,不只限于提供芯片焊接材料的解决方案,同时还提供铝线,铝带和粗铜线,铜带和复合陶瓷基板DBC,DTS(DieTop System)等材料组合方案,为客户提供更优异的功率器件散热解决方案,提高器件的可靠性。除此之外,贺利氏电子还可以为客户提供优良的工程技术服务。贺利氏电子结合材料知识和技术专长,进一步探索客户的产品生产流程及业务上面临的挑战,并且不断开发高品质解决方案,协助客户提升竞争优势。

关键字:贺利氏电子引用地址:功率器件的散热问题,看贺利氏电子从封装角度给的妙招

射频技术面板/显示存储技术电源管理音频/视频嵌入式软件/协议接口/其它便携/移动产品综合资讯论坛惊奇科技词云:

m6米乐在线登录微信订阅号

m6米乐在线登录微信订阅号